# PERFORMANCE CHARACTERISTICS OF CCD SHIFT REGISTERS FABRICATED USING ALUMINUM-ANODIZED ALUMINUM-ALUMINUM DOUBLE LEVEL METALLIZATION\*

D.R. Collins

W.C. Rhines

J.B. Barton

S.R. Shortes

R.W. Brodersen

A.F. Tasch, Jr.

Texas Instruments Incorporated Dallas, Texas 75222

<u>ABSTRACT</u>. The performance characteristics of n-channel 64-bit and 500-bit double-level metallization (Al-Al<sub>2</sub>O<sub>3</sub>-Al) linear surface channel CCD shift registers show excellent charge transfer efficiency, 99.98 percent at 1 MHz. This CTE was achieved on devices on  $929 \,\mu\text{m}^2$  (1.44 mil<sup>2</sup>) per bit area. The stability of these devices is excellent when compared to three-phase single-level metallization devices. A novel double clocking scheme is used to drive the four-phase devices. These results indicate advantages of the Al-Al<sub>2</sub>O<sub>3</sub>-Al metallization system in ease of fabrication, testing, reliability, charge carrying capability, and high-speed operation of large arrays.

## I. INTRODUCTION

Performance characteristics of 64-bit and 500-bit surface channel CCD linear shift registers fabricated with a double-level metallization technique are described in this paper.<sup>1,2,3,4</sup> Both metal levels are standard aluminum and the insulation between the two metallization levels is aluminum oxide formed by anodization. This technique relaxes the 3-µm (0.12 mil) electrode separation tolerance required for single-level metallization, since the thickness of the Al<sub>2</sub>O<sub>3</sub> forms the interelectrode gap. The thickness of the  $Al_2O_3$  ranges from 700 Å to 6,000 Å depending on the particular fabrication procedure used. Due to these extremely narrow gaps, the surface potential is controlled in the region between the electrodes, thus permitting operation with high transfer efficiency. The Al-Al<sub>2</sub>O<sub>3</sub>-Al structure also seals the interelectrode gap from ambient effects and provides an equipotential surface over the interelectrode gap. These devices are not affected by ambient conditions and are very stable, as opposed to single-level metallization devices which are extremely difficult to passivate. No high temperature processing (>500°C) is necessary during the double-level metallization process. Anodization provides a simple, quick method for forming the double-level system insulation. The high conductivity of both levels of metallization in the Al-Al<sub>2</sub>O<sub>3</sub>-Al system allows operation of large CCD arrays at high frequencies. The long RC time constants associated with "resistive seas" or polysilicon electrodes are absent in the Al-Al<sub>2</sub>O<sub>3</sub>-Al system and this allows both higher operating speeds and greater architectural design freedom.<sup>3</sup>

#### **II. DEVICE FABRICATION AND OPERATION**

The fabrication and operation of 8-bit anodized aluminum p-channel shift registers has previously been described.1,3 These devices operated with approximately 99.9 percent CTE at 2 MHz. The electrode lengths were 25.4  $\mu$ m (1.0 mil) and the channel width was 254  $\mu$ m (10 mils) for a bit size of 2.6  $\times$  10<sup>4</sup>  $\mu$ m<sup>2</sup> (40 mil<sup>2</sup>). This paper describes the extension of this technology to the fabrication and operation of both  $64 \times 1$  and  $500 \times 1$  linear shift registers. These devices again used the same four-phase Al-Al<sub>2</sub>O<sub>3</sub>-Al doublelevel metallurgy; in addition, the devices were fabricated using n-channel technology.<sup>5</sup> This n-channel technique allowed higher frequency operation as a result of the increased mobility of electrons, and also decreased the possibility of metal opens by reducing the thick-to-thin oxide transition. The devices were fabricated on (100) p-type (Boron) 40- $\Omega$ -cm silicon. The gate oxide was 1,200 Å in thickness. The electrode length was 7.6  $\mu$ m (0.3 mil) and the channel width was  $30.5 \,\mu\text{m}$  (1.2 mils) for a bit size of 929  $\mu$ m<sup>2</sup> (1.44 mil<sup>2</sup>). The input of a 500 × 1 bit shift

\*This work was supported in part by the U.S. Navy (NAVELEX Contract No. N00039-73-C-0013).

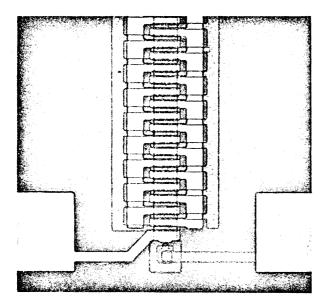

Figure 1. Photomicrograph of the Input of a 500 × 1 4-Phase Anodized Aluminum Double Level CCD Shift Register

register is shown in Figure 1. The input diode, the input gate, and approximately five bits of the shift register are shown. The white electrodes are the input gate and clock electrode phases two and four.

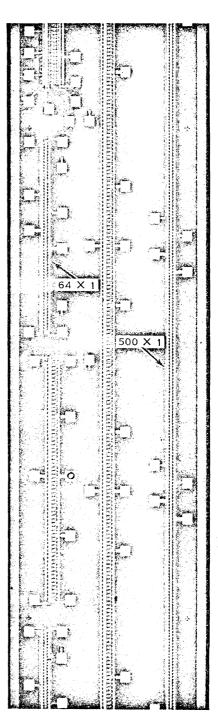

The chip itself contains both the 500  $\times$  1 and the 64  $\times$  1 4-phase anodized aluminum shift registers along with other CCD structures. The artwork for the chip was computer generated at Texas Instruments from cell designs and the resulting computer output was, in turn, fed to a computer-controlled pattern generator. The long length of the 500  $\times$  1 shift register,  $1.53 \times 10^4 \,\mu\text{m}$  (602 mils) required that the photomasks be composed using four reticles. The resulting chip was approximately 8/10 of an inch long-2  $\times 10^4 \,\mu\text{m}$  (800 mils) and a photomicrograph of the chip is shown in Figure 2. Because of the length of the chip, only approximately one-third of the chip appears within the photomicrograph (one-fourth of the chip length extends from cross mark to cross mark).

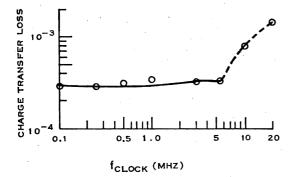

Charge transfer efficiences of 99.98 percent at 1-MHz data rates have been achieved on these surface channel devices with narrow channel widths- $30 \,\mu m$  (1.2 mils). Charge transfer loss (1 - CTE) versus frequency data for a typical device is shown in

80

Figure 3. The measurements were taken with  $\approx 15$ -percent fat zero and the waveforms of the clocks were varied to obtain the maximum transfer efficiency. The data below 10 MHz was taken with 15-volt clocks, while the data at 10 MHz and above was taken with 10-volt clocks, due to driver limitations. The charge transfer efficiency of surface channel devices is known<sup>6</sup> to depend on channel width and the charge transfer efficiency achieved on these Al-Al<sub>2</sub>O<sub>3</sub>-Al devices is essentially equivalent to the best charge transfer efficiency obtained from three-phase surface channel single-level metallization devices of similar geometry and fabrication schedule.

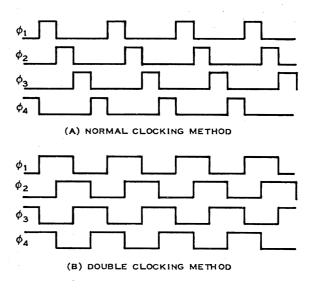

In general, these double-level Al-Al<sub>2</sub>O<sub>3</sub>-Al devices require lower clock voltages and are less sensitive with respect to clock waveforms than single-level metallization devices of similar geometry. Since the electrodes on both metallization levels are coplanar and of equal area with respect to the silicon substrate, novel clocking waveforms may be used to enhance the charge transfer efficiency. Figure 4 shows both the normal four-phase clocking and a new double clocking technique.<sup>7</sup> Consider the normal clocking method for a four-phase system, as shown in Figure 4(a). Each phase has a separate, distinct clock waveform which generates feedthrough. In the system shown in Figure 4(b), however, the clock phases are on for twice the normal duration; therefore, twice the normal amount of charge can be shifted down the register. This not only doubles the size of an output "one" but

also increases the charge transfer efficiency. This increase in charge transfer efficiency occurs because the area under an electrode is void of carriers for only half a clock cycle rather than for three-quarters of a clock cycle. The charge transfer efficiency results described above for the  $Al-Al_2O_3-Al$  devices were obtained using the double clocking technique.

Clock feedthrough into the output of a CCD is an important practical consideration that affects ultimate system noise. Although filtering the output signal at  $f_c/2$  eliminates most of the clock feedthrough, any variation, or "jitter," on the clock lines results in subharmonics which cannot be eliminated by this method. The generation of the clocking pulses in the double clocking technique allows a considerable decrease in drive circuitry complexity because  $\phi_1$  and  $\phi_3$ , along with  $\phi_2$  and  $\phi_4$ , are mirror images of each other. Hence, both  $\phi_1$  and  $\phi_3$  can be generated from a single differential driver; the same situation is true for  $\phi_2$  and  $\phi_4$ . The clock feedthrough suppression possible with the double clocking technique is superior to the normal clocking method since the fact that both  $\phi_1$ and  $\phi_3$  ( $\phi_2$  and  $\phi_4$ ) are generated from the same differential clock generators allows complete cancellation of clock feedthrough at the drivers themselves.

## **III. DISCUSSION**

The  $Al_2O_3$  insulation is also thin enough to suppress the channel potential wells in a buried channel structure. The Al-Al<sub>2</sub>O<sub>3</sub>-Al technique thus provides an attractive alternative to the "resistive sea" approach to buried channel electrode construction. However, in order to perform imaging with an Al-Al<sub>2</sub>O<sub>3</sub>-Al CCD, backside illumination of the CCD is necessary due to the opaque nature of the aluminum structure. In order to maintain resolution in a backside illuminated CCD structure, the device would have to be thinned to a thickness of approximately the centerto-center spacing of the resolution elements  $\approx 30 \,\mu m$ (1.2 mils). However, thinning a device to this thickness is also necessary for either a front or backside illuminated CCD in the near infrared where the absorption coefficient of radiation is quite low in Si ( $\approx 5 \text{ cm}^{-1}$  at 1- $\mu$ m wavelength). While thinning imposes additional fabricational difficulties, the backside illumination of an imager would optimize the

sensitivity from two standpoints: (a) there is no metal on the backside to reflect the incident illumination and (b) optimum antireflection coatings (such as SiO) may be used on the backside. Antireflection coatings on the front side of a CCD are less than optimum since the CCD requires  $\approx 1,200$  Å of gate insulator with a nonideal index of refraction to operate electrically. Furthermore, any polysilicon or glass overcoat layers will further reduce the quantum efficiency of the device.

Another option opened with a thinned CCD is the possibility of operating in the electron-bombarded silicon (EBS) mode. Theoretical calculations indicate that an EBS mode CCD operating at room temperature should be approximately 5 to 10 times more sensitive than a cooled (210K) CCD without the EBS stage. Thus, the ideal CCD area imager fabrication technique appears to be a backside illuminated, thinned, buried channel, anodized aluminum doublelevel metallization structure.

# REFERENCES

- D.R. Collins, S.R. Shortes, W.R. McMahon, T.C. Penn and R.C. Bracken, "Double Level Anodized Aluminum CCD," presented at the International Electron Devices Meeting, 6 December 1972, Washington, D.C., p. 168 of the 1972 *IEDM Technical Program* (IEEE Cat. No. 72 CHO702-1ED).

- D.R. Collins, J.B. Barton, D.D. Buss, A.R. Kmetz and J.E. Schroeder, "CCD Memory Options," presented at the International Solid State Circuits Conference, 15 February 1973, Philadelphia, Pa., p. 136 of the *Digest of Technical Papers* (IEEE Cat. No. 73 CHO711-2ISSCC).

- 3. D.R. Collins, S.R. Shortes, W.R. McMahon, R.C. Bracken and T.C. Penn, "Charge-Coupled Devices Fabricated Using Aluminum-Anodized Aluminum Aluminum Double-Level Metallization," Journal of the Electrochemical Society, Vol. 120, pp. 521-526 (1973).

- W.C. Rhines, D.R. Collins, J.B. Barton and S.R. Shortes, "Fabrication of Double-Level Charge-Coupled Devices Using Aluminum Anodization," presented at SEMICON III, San Mateo, California, 22 May 1973.

- 5. R.H. Wakefield, E.R. Ward and J.A. Cunningham, "Another Self-Aligning MOS Process Has Interconnecting Advantages," *Electronics*, 3 January 1972.

- 6. W.F. Kosonocky and J.E. Carnes, "Two-Phase Charge-Coupled Devices with Overlapping Polysilicon and Aluminum Gates," *RCA Review*, Vol. 34, pp. 164–202 (1973).

- 7. This double clocking technique was first suggested in a private communication from C.H. Séquin.