### 1 GHz Multiple Output 128x256 Element Area Array

Bill D. Washkurak and Savvas G. Chamberlain

DALSA INC. 605 McMurray Road Waterloo, Ontario, N2V 2E9 Phone: (519) 886-6270 Fax: (519) 886-8032

#### Abstract

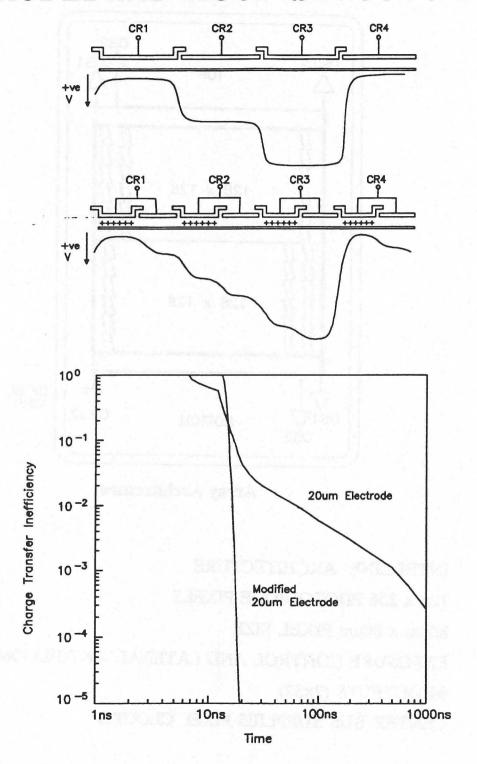

A high speed imager capable of a 1 Gigahertz frame rate was developed with 80µm x 80µm pixels. A photodiode, interline transfer pixel architecture is used with lateral antiblooming and exposure control capability. A special multi-phase readout shift register and parallel to serial transfer structure are designed for high charge transfer efficiency operation across a large 80µm pitch at high speed. The charge transfer efficiency is modelled analytically as well as with a 2-dimensional transient device simulator for both a conventional 4 phase and the special multiphase shift register.

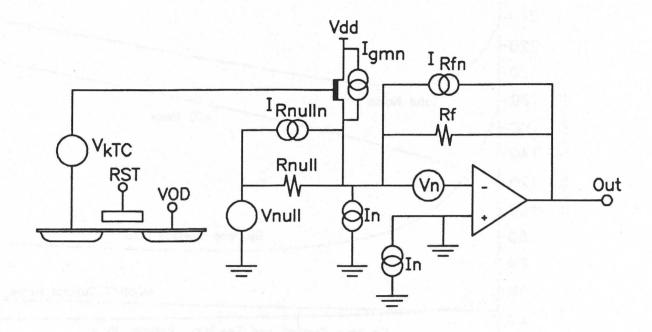

A total of 64 outputs each designed to operate at 16 MHz are distributed around the array. In order to minimize power dissipation, a single output MOSFET operating in conjunction with an off-chip transimpedance amplifier was used. The configuration is compared to a conventional two stage source follower with respect to bandwidth, noise and physical size.

**Array Architecture**

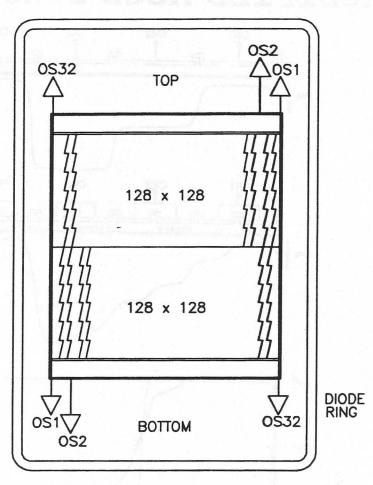

- INTERLINE ARCHITECTURE

- 128 x 256 PHOTODIODE PIXELS

- 80μm x 80μm PIXEL SIZE

- EXPOSURE CONTROL AND LATERAL ANTIBLOOMING

- 64 OUTPUTS (2x32)

- CENTER BUS SUPPLIES PIXEL CLOCKS

# MODIFIED HCCD STRUCTURE

## **OUTPUT CIRCUIT**

$$S_o = S_{fd}G_mR_f$$

- A 25μm/5μm ON-CHIP SINGLE MOSFET IS CONNECTED TO AN OFF-CHIP OPAMP YIELDING A CURRENT MODE HIGH SPEED (10ns EDGES) CONFIGURATION THAT OCCUPIES LITTLE PHYSICAL SPACE ON-CHIP

- USING THE TRANSIMPEDANCE APPROACH WITH A 4000Ω

FEEDBACK RESISTOR THE TOTAL CONVERSION EFFICIENCY IS

2.4µV/e COMPARED TO 0.8µV/e IF THE ON-CHIP MOSFET IS

CONFIGURED AS A SOURCE FOLLOWER WITH A MUCH LOWER

BANDWIDTH

- CONFIGURATION OPERATES WITH REDUCED ON-CHIP POWER DISSIPATION

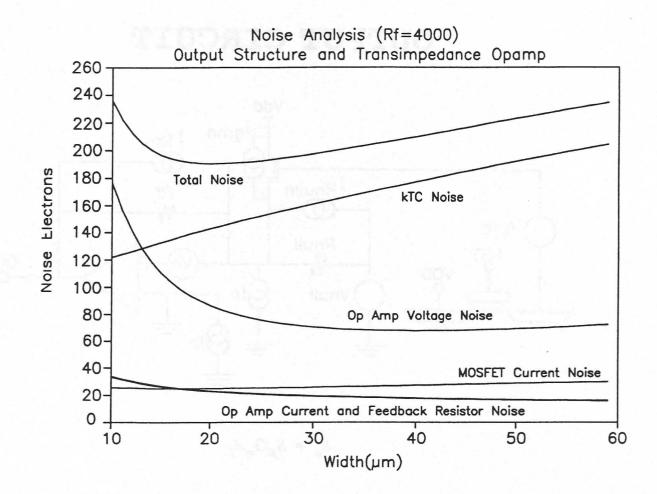

- PLOT OF FLOATING DIFFUSION NOISE ELECTRONS TO MOSFET WIDTH (LENGTH = 5μm)

- AT W = 25μm NOISE IS AT ITS MINIMUM 190 ELECTRONS

- AS W INCREASE BEYOND 25μm, kTC NOISE DOMINATES

- IF CDS IS USED TO ELIMINATE KTC COMPONENT, A LARGER W INCREASES GM AND THUS TOTAL CONVERSION EFFICIENCY

- FOR HIGH SPEED OPERATION, NOISE IS COMPARABLE TO A TWO STAGE SOURCE FOLLOWER