#### The State-of-the-Art of Mainstream CMOS Image Sensors

Ray Fontaine

Senior Technology Analyst, Competitive Technical Intelligence Group, Chipworks, Inc. 1891 Robertson Road, Suite 500, Ottawa, ON K2H 5B7, Canada

Email: <u>rfontaine@chipworks.com</u> Phone: (613) 829-0414

Abstract - The steady growth of mobile phones sales (feature and smartphones) has been the primary driver for CMOS image sensor (CIS) unit shipment growth over the last 3-5 years. As CIS market revenue has grown, so have R&D spending and patent filings. This effort has resulted in advanced mobile camera systems containing phase detection pixel arrays for fast autofocus (AF), ~1 µm generation pixels with improved low-light sensitivity, advanced chip-stacking, featuring a back-illuminated CIS wafer joined with an image signal processor (ISP) wafer, and video recording up to 4K. Innovation for smartphone cameras will continue, although given the competition for these high-volume sockets, many IDMs and fabless companies are developing chips for emerging, higher margin imaging applications such as automotive, security, medical, etc. These emerging opportunities are driving technology transfers from mobile imaging to these growth areas.

#### I. IMAGE SENSOR MARKET CONDITIONS

The market for imaging chips continues to be in a growth phase. The consensus of many market research firms for the 2014 CIS market size is about \$9 billion USD. Yole has predicted a 10.6% CAGR for the CIS market from 2014 to 2020 [1]. Of this total, it is estimated that Sony, Samsung, and OmniVision hold about two-thirds revenue market share, driven primarily by mobile phone and tablet camera chips. The mobile imaging market is expected to grow at a 13% CAGR from 2014 to 2020. The current market pull for mobile imaging systems includes: improved image quality, reduced power consumption, and faster AF.

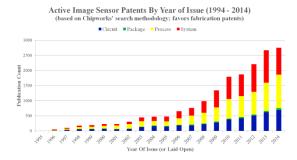

## II. INVENTIONS: A BENCHMARK OF SECTOR MATURITY

Imaging companies, like all semiconductor companies, do face a number of risks. One risk is the potential for technology convergence leading to consolidation of overall market share, or for disruption within a sub-sector. Fortunately, the strong image sensor patenting growth trend [2] suggests continued opportunities for differentiated products.

Fig. 1: Image Sensor Patent Trend Analysis (Favors Process Patents)

### III. EVOLUTIONARY TECHNICAL EVENTS: ISOLATION SCHEMES, PHASE PIXELS, NON-BAYER CFA

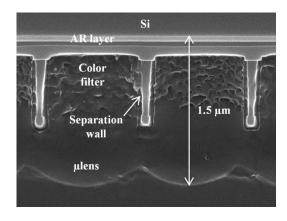

Most of the imaging chips designed in to marquee consumer products have used incremental evolutions of concepts. Noteworthy pixel structural existing optimizations include optical stack thinning and crosstalk suppression techniques. Panasonic's SmartFSI [3], which features light separation walls between the color filters of front-illuminated pixels, is a concept that has been adapted to recent back-illuminated CIS chips. The closest example is ON Semiconductor's (Aptina) Clarity+ chips, which feature color filters embedded in cavities etched in a blanket oxide film deposited over the back surface [2]. This structure, in effect, creates a per-pixel light pipe while matching the 1.5 µm record for optical stack thinness. The device analyzed does not use a metal aperture grid, but instead relies on the light pipe effect and microlenses for optical isolation.

Fig. 2: ON Semiconductor (Aptina) AR0842 Clarity+ 1.1 µm Pixel

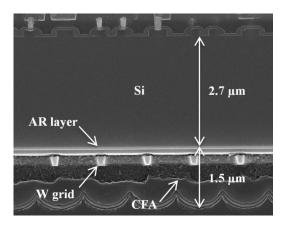

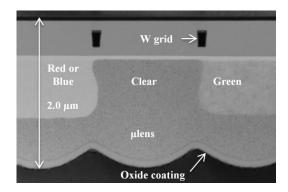

Sony and Samsung both use a back metal aperture grid and have similarly adapted the SmartFSI-like structure by embedding color filters into the grid metal. Previous generations from each manufacturer had used a gap-filling organic buffer layer beneath the CFA. Sony's implementation of embedded filters has resulted in a 1.5 µm thick optical stack for the co-record optical stack thinness (based on Chipworks' analysis) [4]. As reported by Sony [5], thinning the optical stack has improved the sensitivity of edge pixels.

Fig. 3: Sony IMX214, 1.12 µm Pixel, Embedded Color Filter Array

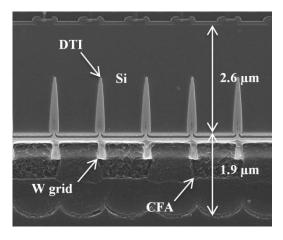

Samsung's embedded color filters are comparatively thicker, resulting in a 1.9 µm optical stack thickness [6]. However, its strategy is to combine embedded filters with first generation deep trench isolation (DTI) technology to reduce electrical and optical cross-talk in the substrate. The first generation isolation trenches penetrate about 1.6 µm deep into the back of a 2.6 µm thick substrate. A hafnium oxide-based trench fill provides a charge trapping layer to passivate the Si surface and also serves as an anti-reflective layer. Samsung has announced further work to fully isolate each pixel with its ISOCELL technology [7].

Fig. 4: Samsung S5K2P2XX, 1.12 µm Pixel, Partial DTI

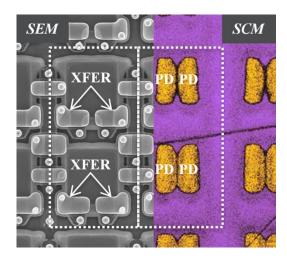

The majority of phase detection systems rely on metal masking of proximate pixel pairs embedded in front- and back-illuminated active pixel arrays. A notable exception is Canon's dual photodiode solution which features four photodiodes per two shared pixels [8].

Fig. 5: Canon LC1290A (EOS-70D) 4.1  $\mu m$  Dual Pixel CMOS AF

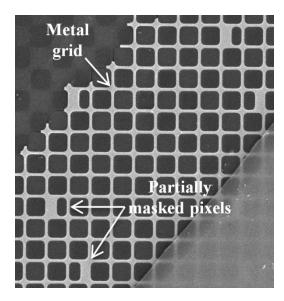

For those manufacturers with experience in constructing back-illuminated pixel aperture grids, the fairly recent requirement for phase detection pixel systems has been straightforward to address at the chip level. Examples of half-masked phase pixel pairs and multi-aperture phase pixels are in production. Green or clear filters are preferred for 1.4  $\mu$ m and 1.12  $\mu$ m generation phase pixels, while Sony has shifted from the green to blue channel for phase pixels on its 3.9  $\mu$ m pixel generation APS-C chips [2].

Fig. 6: Sony 8 MP, 1.5 µm 'Focus Pixels' from Apple iPhone 6 Plus

A substantial amount of engineering effort has also been directed towards the introduction of panchromatic pixels.

Both ON Semiconductor (Aptina) and OmniVision had design wins with 1.1  $\mu m$  generation sensors using non-Bayer color filter arrays, however both required the use of a custom ISP at the systems level. The AR0842 features Clarity+ technology comprising a mix of 25% red, 25% blue, and 50% clear pixels [2]. OmniVision has incorporated diagonal rows of clear pixels into its proprietary RGB Clear color filter mosaic. Adjacent rows include a diagonal green channel and alternating pairs of blue and red filters.

Fig. 7: OmniVision OV10820 RGB Clear (RGBC) 1.4 µm Pixel

# IV. DISRUPTIVE TECHNICAL EVENT: THE EMERGENCE OF THE STACKED CHIP CIS

The motivations for investing in stacked chip CIS development are somewhat varied depending on manufacturer [10], but can be summarized as: adding functionality, decreasing form factor, enabling flexible manufacturing options, and facilitating optimization for each die in a 3D stack.

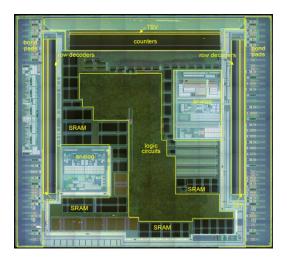

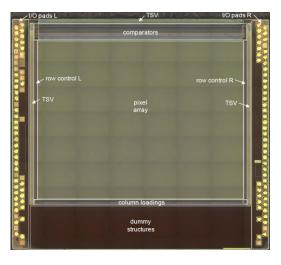

Sony announced the world's first stacked chip CIS camera systems for consumer electronics in 2012 [11] and 8 MP ISX014 chips were found in a tablet computer in early 2013 [12]. The first generation chips employ vialast TSVs to connect pads from the Sony-fabricated, 90 nm generation CIS die to landing pads on a Sonyfabricated, 65 nm generation ISP. The die stack was partitioned such that most of the functionality of a conventional system-on-chip (SoC) CIS was implemented on the ISP die; the CIS die retained the active pixel array, final stage of the row drivers, and comparator portion of the column-parallel ADCs [13] [14]. Note that due to the mix of design rules, the comparator blocks on the CIS die are pixel pitch matched, while the companion column circuits on the 65 nm ISP die occupy a footprint about 25% narrower than the active pixel array.

Fig. 8: Sony ISX014 8 MP Stacked CIS - ISP Die at Poly Level

Fig. 9: Sony ISX014 8 MP Stacked CIS - CIS Die at Poly Level

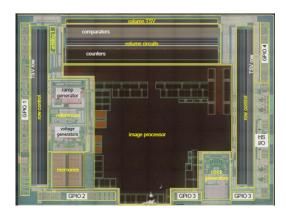

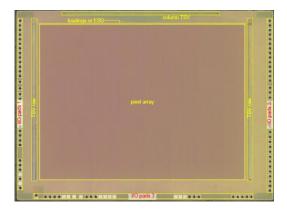

Sony's 13 MP IMX214 second generation stacked CIS chips were similarly fabricated using its 90/65 nm (CIS/ISP) technology generation. However, in a continuation of its FLAT technology [14], first introduced in 2011 and observed in all small-pixel back-illuminated chips since, Sony simplified the IMX214 wafer flow by removing the STI process module entirely. The key work on the second generation stacked process was to evolve the CIS silicon for use solely as the active pixel array substrate and moving the entire column readout chain and peripheral transistors off-die to the underlying ISP.

In 2014 Sony demonstrated flexibility in choice of wafer vendors afforded by chip stacking by using TSMC as a foundry for the ISP on the Apple iPhone 6/6 Plus iSight cameras. These chips incorporate Sony 90 nm CIS wafers and TSMC 40 nm ISP wafers [2].

Fig. 10: Sony IMX214 13 MP Stacked CIS - ISP Die at Poly Level

Fig. 11: Sony IMX214 13 MP Stacked CIS - CIS Die at Poly Level

Samsung and OmniVision have both been sampling small-pixel, stacked chip CIS and both are expected to have secured design wins within 2015. Highlights of near-term stacked chip product announcements include: >20 MP resolution, high-dynamic range, and on-chip phase detection pixel array. Additionally, OmniVision has announced the world's first 1.0 µm pixels [16] in a stacked chip process.

Given the continued, aggressive stacked CIS development underway from independent device manufacturers (IDM) and foundries it's predictable that stacked chip adoption will occur very rapidly over the next few years.

#### V. REFERENCES

- [1] P. Cambou, J. Jaffard, "Status of the CMOS Image Sensor Industry 2015 Report", February 2015

- R. Fontaine, et al., ChipSelect for Image Sensors (ChipSelectIS) Subscription Service, Chipworks

- H. Watanabe, et al., "A 1.4µm front-side illuminated image sensor with novel light guiding structure consisting of stacked lightpipes", IEDM 2011

- R. Krishnamurthy, et al., "Sony IMX214 Second Generation 13 MP Exmor RSTM Stacked BSI CIS with SME-HDR Imager Process Review", Chipworks, March 2015

- "IMX214 Diagonal 5.867 mm (Type 1/3.06) 13.13M-Effective Pixel Stacked CMOS Image Sensor", Sony product literature

- R. Krishnamurthy, et al., "Samsung S5K2P2XX 16 MP, 1.12 µm Pixel Size Back-Illuminated ISOCELL CIS from the Samsung Galaxy S5 Smartphone Primary Camera Imager Process Review", Chipworks, May 2014

- J. Ahn, et al., "A 1/4-inch 8Mpixel CMOS Image Sensor with 3D Backside-Illuminated 1.12µm Pixel with Front-side Deep-Trench Isolation and Vertical Transfer Gate", ISSCC 2014

- W. Machado, et al., "Canon LC1290A (Die Markings) 20.2 Mp, 4.1 µm Pixel Size Dual Pixel CMOS AF APS-C CMOS Image Sensor from the Canon EOS-70D(W) DSLR Camera Imager Process Review", Chipworks, October 2013

- L. Rezaee, et al., "OmniVision OV10820 10.5 Mp, 1.4 µm Pixel Pitch RGB Clear (RGBC) Color Filter Back Illuminated (BSI) CMOS Image Sensor from the Motorola Moto X Smartphone Imager Process Review, Chipworks, November 2013

- [10] L. Grant, "Evolution of 3D Integration for CMOS Image Sensor Cameras", Image Sensors 2014

- [11] "Sony Develops "Exmor RS," the World's First\*1 Stacked CMOS Image Sensor", Sony Corporate Press Release, August 2012

- [12] P. Jagodzinski, et al., "Sony ISX014 ¼ Inch 8 Mp, 1.12 µm Pixel Size Exmor RS Stacked Back Illuminated CIS Imager Process Review", Chipworks, March 2013

- [13] S. Sukegawa, et al., "A 1/4-inch 8Mpixel Back-Illuminated Stacked CMOS Image Sensor", ISSCC 2013"

- [14] K. Itonaga, et al., "Extremely-Low-Noise CMOS Image Sensor with High Saturation Capacity", IEDM

- [15] B. Liu, et al., "Sony IMX135 Exmor RS™ 13 Mp Stacked CMOS Image Sensor Circuit Analysis of Row Control, Column Data Readout and Control, and Ramp Generator", Chipworks, March 2014

[16] "OV16880 16 MP Product Brief" OmniVision

- product literature