## POLITECNICO MILANO 1863

## NIR SPADs and fast-gating circuits

## Alberto Tosi and SPADIab colleagues

1<sup>st</sup> International SPAD Sensor Workshop – ISSW 2018 Les Diablerets, February 26<sup>th</sup>, 2018

## InGaAs/InP SPAD

Outline

- Device structure

- Performance

- Circuits for InGaAs/InP SPAD

- SPAD with integrated quenching resistor

- GHz sinusoidal gating

- Integrated fast-gated active quenching circuit (ASIC)

# InGaAs/InP SPAD

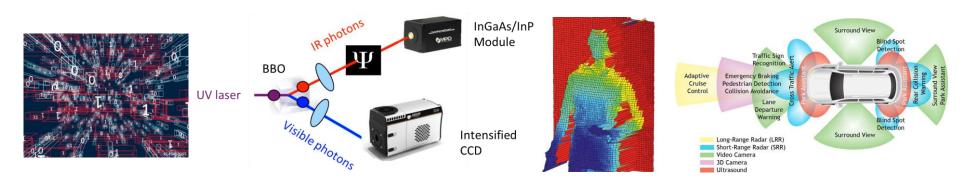

## Single-photon counting in the NIR (1 – 1.6 $\mu$ m)

- Quantum Information Processing and Communication

- Quantum Key Distribution (QKD)

- Eye safe ranging (LIDAR)

- Unconventional (ghost, non-line-of-sight, ...) imaging

- Time-resolved diffused optical spectroscopy

- Photodynamic therapy (PDT) for cancer treatment

- Optical testing of VLSI circuits

- Photonics research in the 1  $\mu$ m 1.6  $\mu$ m range

### Detector + electronics tailored for the specific application!

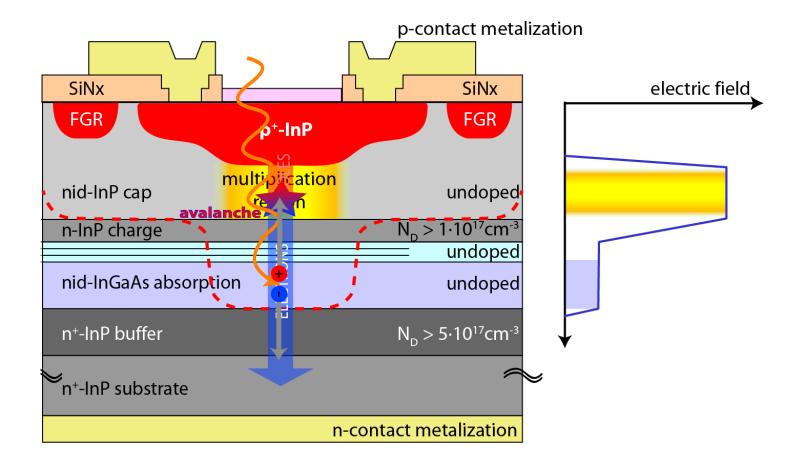

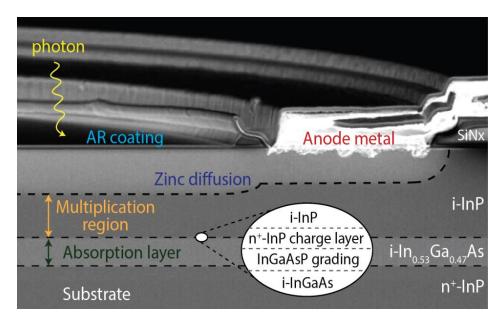

#### InGaAs/InP SPAD

Photons up to ~ 1.6  $\mu$ m  $\rightarrow$  E<sub>g</sub> < 0.8 eV  $\rightarrow$  **InGaAs** (E<sub>g</sub> ~ 0.75 eV) But low E<sub>g</sub> means:

- higher noise  $\rightarrow$  **cooling** is mandatory (T ~ 230 K)

- strong tunneling → higher E<sub>g</sub> material is required for avalanche

→ InP with E<sub>g</sub> ~ 1.35 eV

### Separate Absorption, Charge and Multiplication (SACM)

• Absorption:

$In_{0.53}Ga_{0.47}As$   $(E_g \sim 0.75 \text{ eV})$

• Charge:

highly-doped InP

$(E_g \sim 1.35 \text{ eV})$

• Multiplication:

InP

$(E_g \sim 1.35 \text{ eV})$

Planar technology (no MESA) for lower noise and higher reliability Front-illuminated structure  $\rightarrow$  Well-defined collection area Back-illuminated structure  $\rightarrow$  Suitable for arrays

### InGaAs/InP SPAD

(Front-illuminated structure)

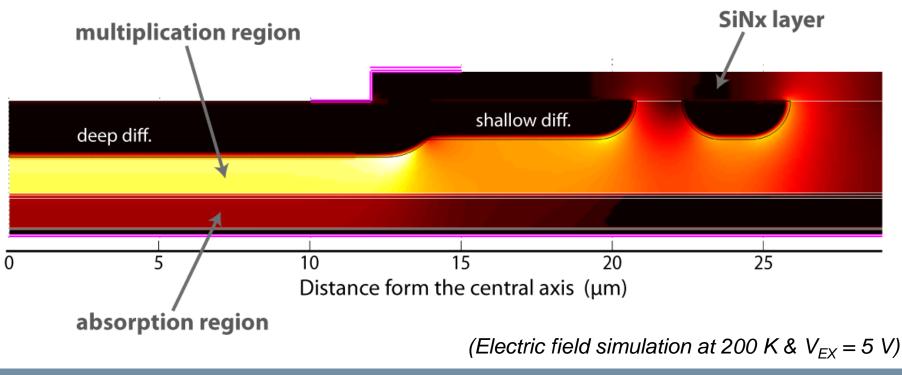

## Design of InGaAs/InP SPAD

Optimized double Zn diffusion (depths and diameters)

- good uniformity in the active area ( $\Delta V_{BD}$  < 4%)

- no activation in the periphery

## → Uniform sensitivity and low timing jitter

(SEM cross-section)

(top view)

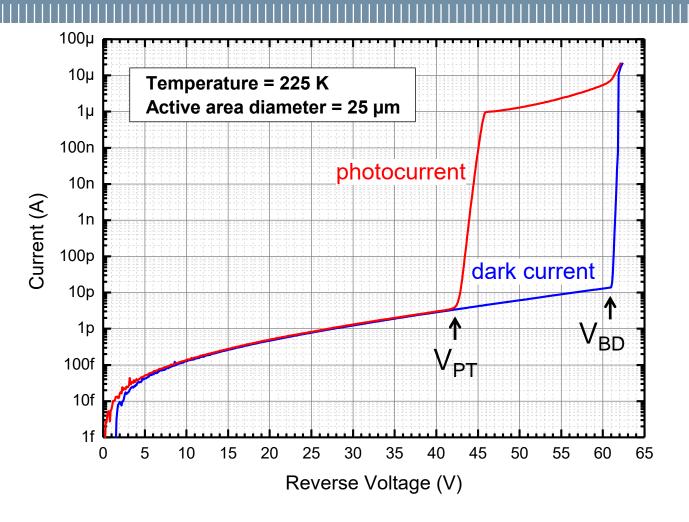

#### I-V curve at low temperature

**Low dark current**:  $I_{dark} \sim 10 \text{ pA} @ V_{BD} - 1 \text{ V}$ , sharp breakdown knee, large  $V_{BD} - V_{PT}$  difference

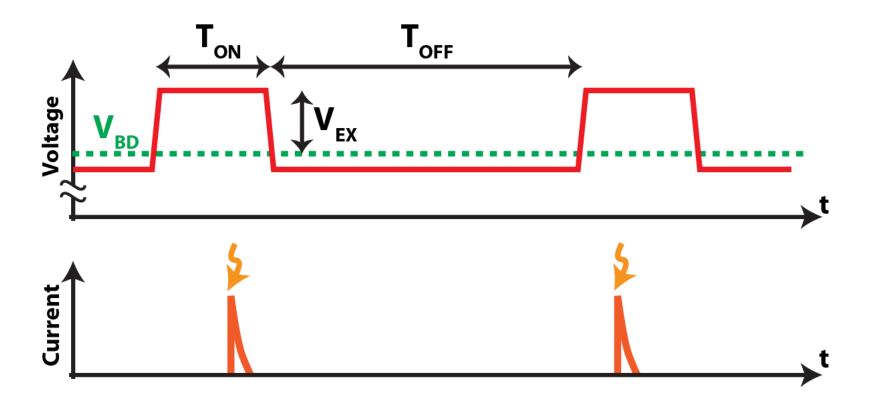

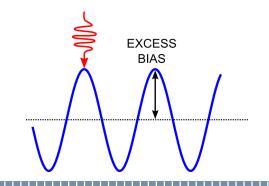

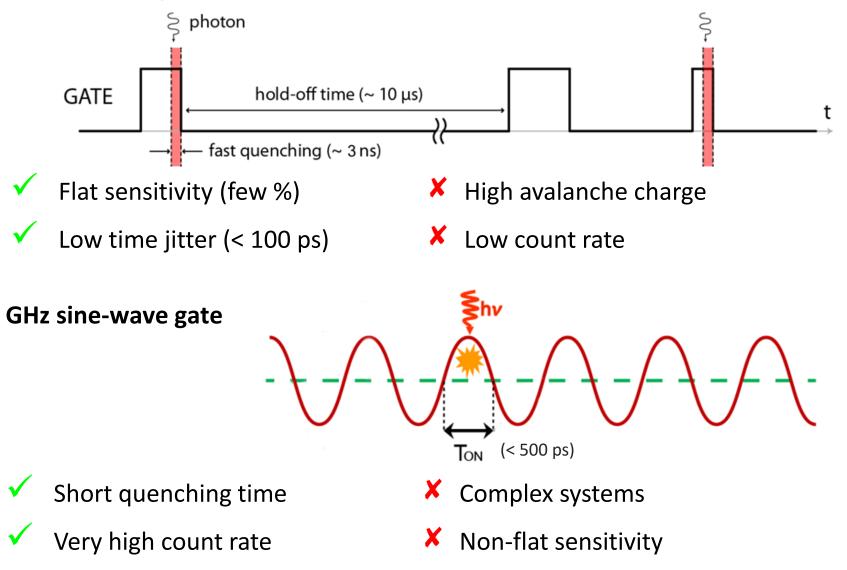

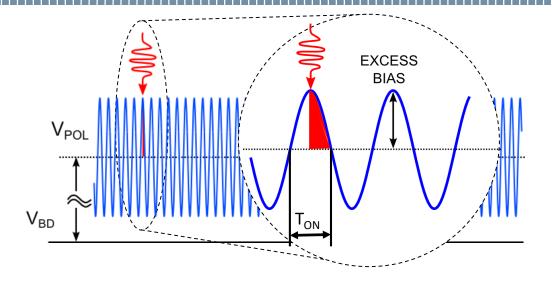

#### **Gated-mode operation**

- SPAD is enabled during Gate-ON time

- SPAD is held OFF to empty traps  $\rightarrow$  reduce afterpulsing

- Gate period  $T_{GATE} = T_{ON} + T_{OFF}$

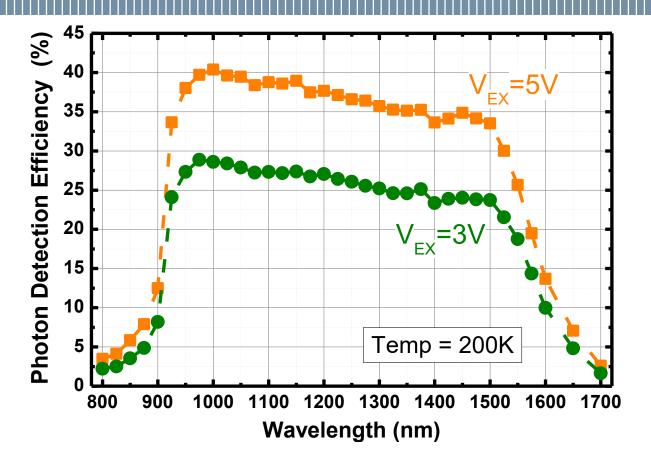

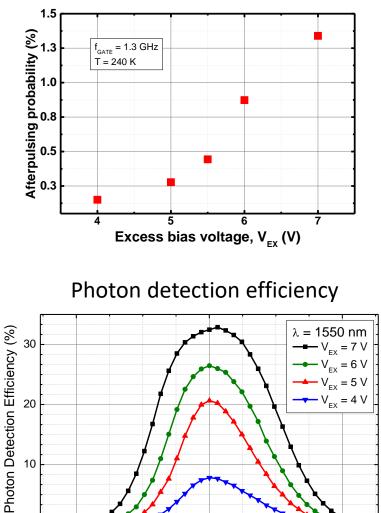

## **Photon detection efficiency**

Good photon detection efficiency:

- -40% @  $\lambda = 1000$  nm,  $V_{EX} = 5$  V

- -25% @  $\lambda = 1550$  nm,  $V_{EX} = 5$  V

- still 3% @  $\lambda$  = 1700 nm, V<sub>EX</sub> = 5 V

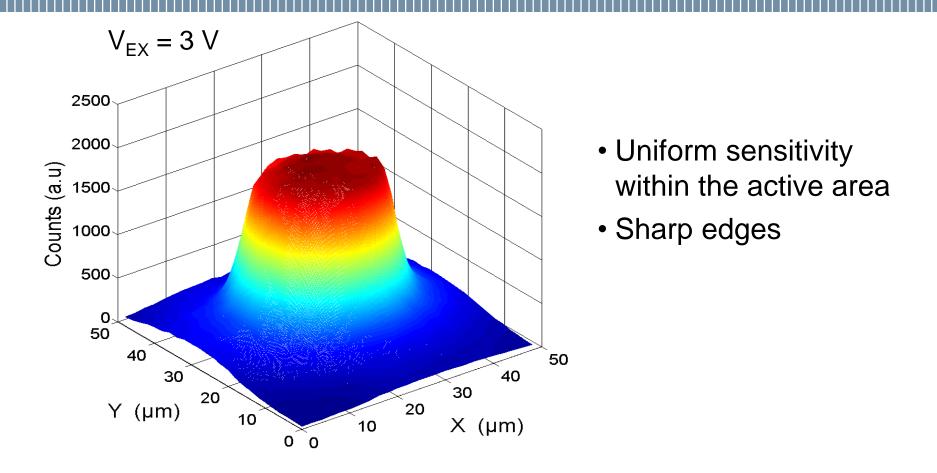

## Active area uniformity

Uniformity improves at higher excess bias (due to saturation of avalanche triggering probability)

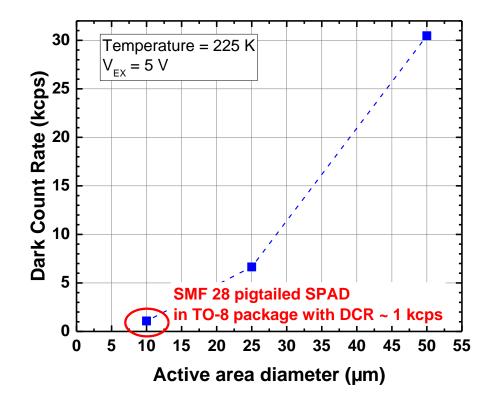

### Low dark-count-rate InGaAs/InP SPAD

- DCR scales with active area → bulk origin (while dark current scales with perimeter, i.e. it is peripheral leakage)

- 10 µm InGaAs/InP SPAD with DCR of few kcps

- 10 μm SPADs have been fiber pigtailed (Micro Photon Devices MPD)

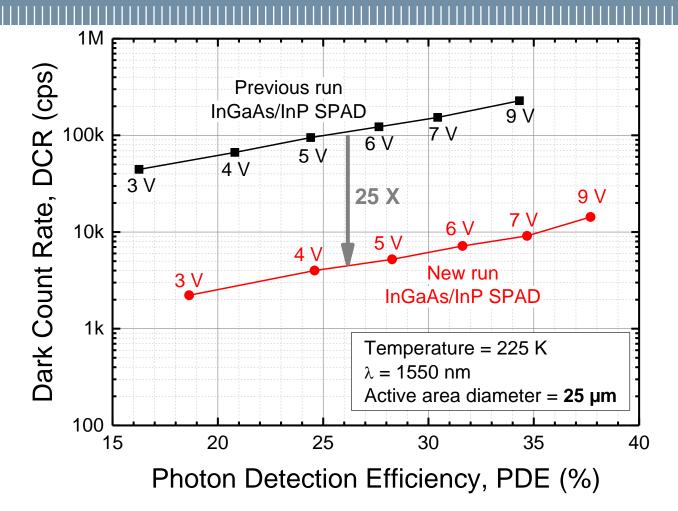

## Impact of design on dark count rate

**25 times lower DCR at a given PDE** by improving SPAD design → There is room for further improvement!

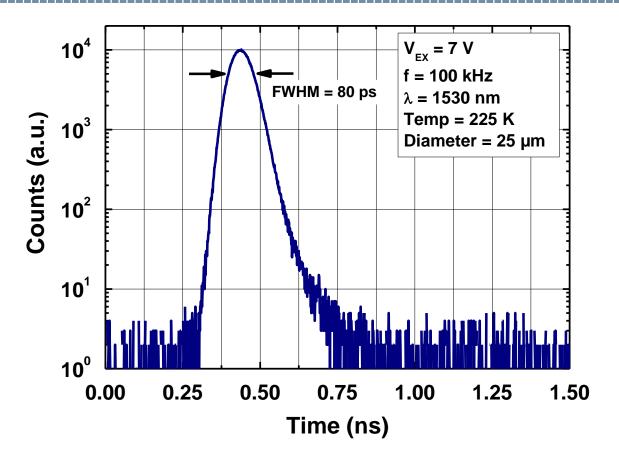

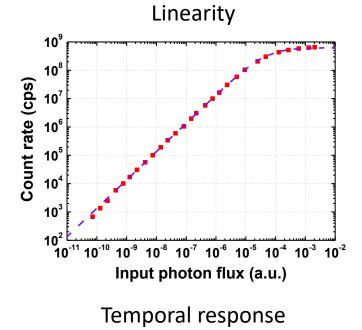

## **Temporal response**

Sharp and "clean" time response FWHM < 80 ps @ 7 V

- Near Gaussian distribution

- Short exponential tail ( $\tau$  = 58 ps)

ISSW 2018 – February 26, 2018 – alberto.tosi@polimi.it

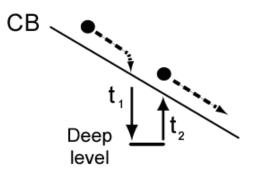

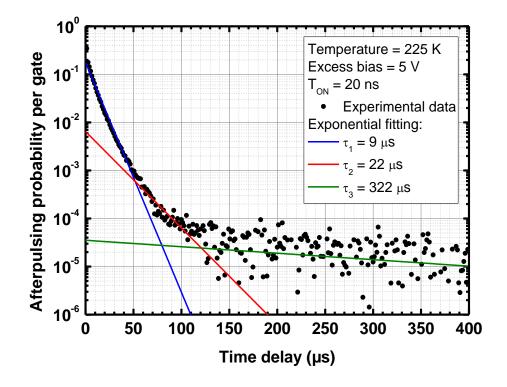

## Afterpulsing

Main drawback of InGaAs/InP SPADs: afterpulsing

- Some avalanche carriers get trapped in deep levels in InP multiplication region

- Delayed release triggers "afterpulse" avalanches

### Limitation to maximum count rate

Here is an example where different traps release carriers with different time constants (10's or even 100's µs!)

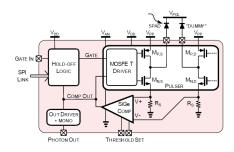

Circuits for high count rate InGaAs/InP SPAD systems

## Afterpulsing reduction techniques for higher count rate 18

#### **Reduce concentration of deep levels**

$\rightarrow$  challenging task (improved fabrication process)

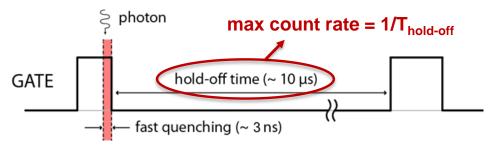

#### Long hold-off time before re-arming

$\rightarrow$  not an option at high rates

#### **Reduce avalanche carriers**

fast quenching (monolithically integrated passive quenching or ASIC)

- $\rightarrow$  either gated or free-running mode

- $\rightarrow$  moderately high count rates (1–10 MHz)

- **short gates** (<< 1 ns):  $\rightarrow$  very high (> 100 MHz) count rates

- $\rightarrow$  complex RF transients suppression

$\rightarrow$  non-flat sensitivity

#### **POLITECNICO** MILANO 1863

TON

ISSW 2018 – February 26, 2018 – alberto.tosi@polimi.it

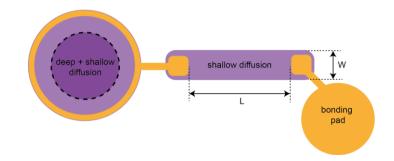

## SPAD with integrated quenching resistor

## SPAD with integrated quenching resistor

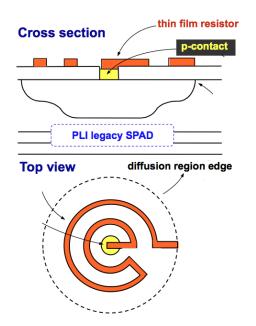

#### Others' implementation (PLI NFAD):

- Thin film resistors (up to MΩ)

- Additional fabrication steps and masks required

- Slow re-arm (100 ns ÷ 1 µs)

#### **PoliMi implementation:**

- No additional fabrication steps: Zn shallow diffusion exploited

- kΩ resistor: quasi-quenching

faster re-arm (< 100 ns)</li>

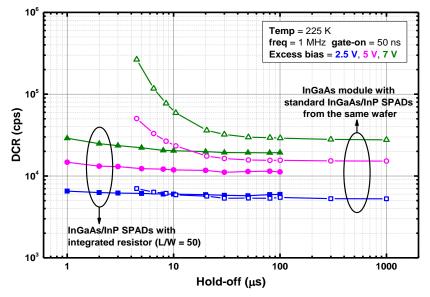

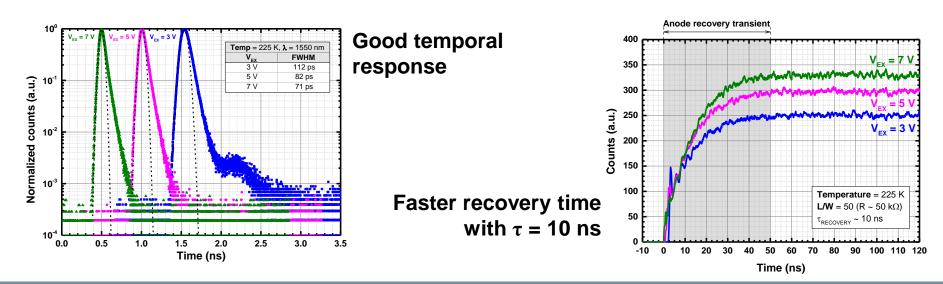

## Afterpulsing of InGaAs/InP SPAD with integrated resistor 21

### Significant afterpulsing reduction

ISSW 2018 – February 26, 2018 – alberto.tosi@polimi.it

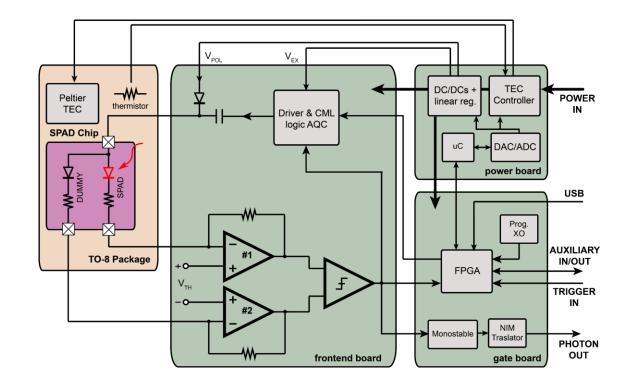

## Design of a compact module 22

Detector, front-end electronics and cooling housed in a small case

- Easy integration in optical setups

- Easy to use and configurable

## GHz sinusoidal gating with SPAD-dummy balancing approach

### Gating of InGaAs/InP SPADs

#### Square-wave gate

ISSW 2018 – February 26, 2018 – alberto.tosi@polimi.it

## **Gigahertz sinusoidal gating - requirements**

Gate signal at  $f_G > 1$  GHz for fast avalanche quenching  $f_G$  tunable in a wide range (900-1400 MHz) for:

- Synchronization with different external laser systems

- Best trade-off between afterpulsing and detection efficiency

#### Adjustable excess bias:

- for optimizing PDE, DCR, afterpulsing, timing jitter

- Up to 7 V (27 dBm!)

#### Long-term stability

Feedback for gate feed-through rejection

#### Suitable for rack mounting

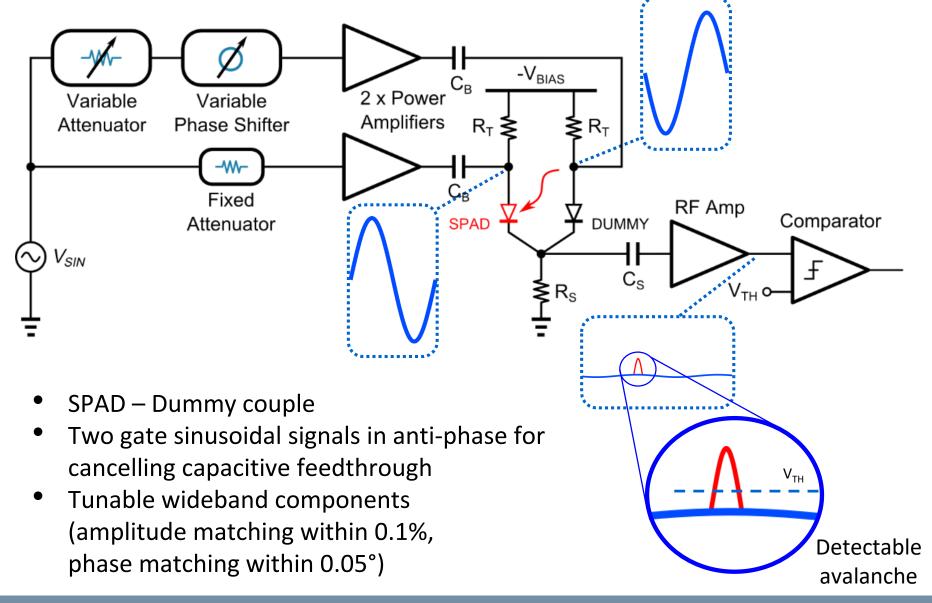

## PoliMi "SPAD-dummy" balanced configuration

26

## Gigahertz sinusoidal gating of InGaAs/InP SPAD

## **PoliMi sine-wave gate results:**

(compared to square-gate system with similar SPAD)

| At the same low afterpulsing probability: |                                | 1.5 %    | 1.5 % (*)  |

|-------------------------------------------|--------------------------------|----------|------------|

| ✓                                         | Very high count rate           | 650 Mcps | < 100 kcps |

| $\checkmark$                              | Good peak detection efficiency | ~ 30 %   | ~ 30 %     |

| $\checkmark$                              | Narrow temporal response       | < 70 ps  | < 70 ps    |

All results with 7 V excess bias unless specified – (\*)  $T_{_{ON}}$  = 5 ns,  $T_{_{HO}}$  = 10  $\mu s$

### Gigahertz sinusoidal gating of InGaAs/InP SPAD

Afterpulsing probability

ISSW 2018 – February 26, 2018 – alberto.tosi@polimi.it

-25

0

Time (ps)

25

50

75

100

125

-75

-125

-100

-50

160 mm

Main board of the new system:

- All the basic blocks on board:

- Gate generation

- Gate amplification

- Avalanche readout

- Feedback control system

- PLL with multiple outputs generates both gate signals (800 – 1500 MHz)

- Programmable gain amplifier to set gate amplitude (up to  $V_{EX} = 7 \text{ V}$ )

- Readout amplifiers with 3 GHz bandwidth and ultrafast comparator

SiGe integrated circuit for fast gating SPADs

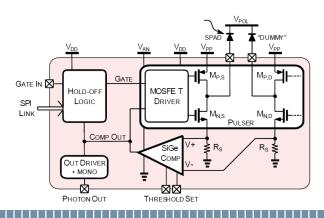

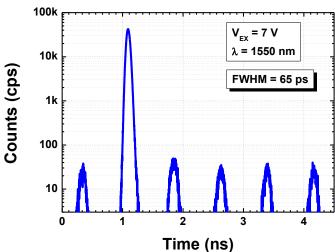

## Integrated fast-gated active quenching circuit (ASIC)

### Integrated circuit (SiGe BiCMOS technology):

- SPAD front-end based on "SPAD-dummy" approach

- Quenching time < 1 ns

- Very fast transition times (< 200 ps @  $V_{EX}$  = 5 V)

- High repetition rate (up to 250 MHz)

- Low timing jitter (FWHM < 90 ps with InGaAs/InP SPAD, intrinsic < 20 ps)

- Mounted in a 12 pin TO-8 package  $\rightarrow$  compact module

- Ready for arrays!

31

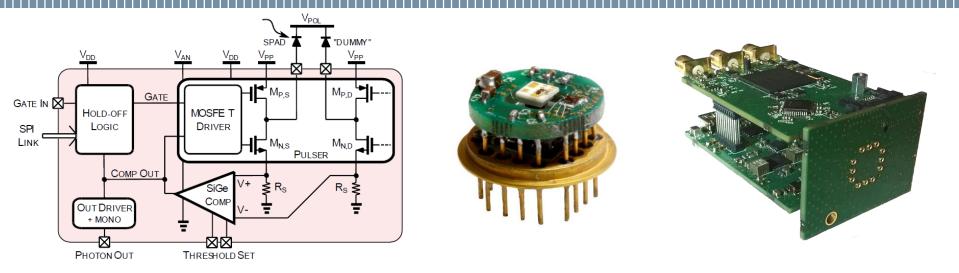

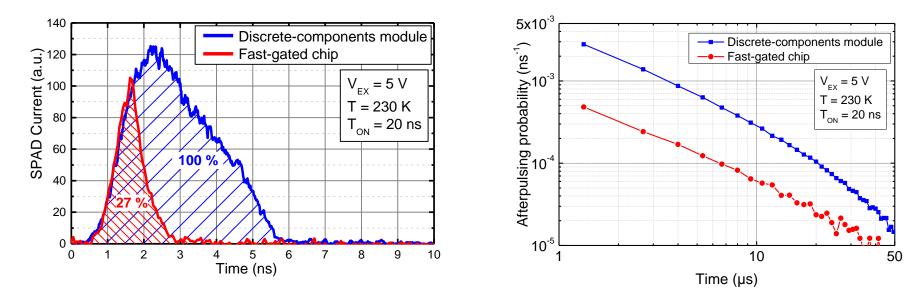

## Integrated fast-gated active quenching circuit 32

- Very fast rise/fall edges (< 200 ps @  $V_{EX}$  = 5 V)  $\rightarrow$  short gate (300 ps)

- Flat sensitivity (±15%) inside long gate windows

- Free-running mode available

## Integrated fast-gated active quenching circuit 33

## Effective reduction of avalanche charge → lower afterpulsing even with long gate

5X reduction of afterpulsing with long gate

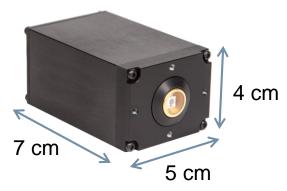

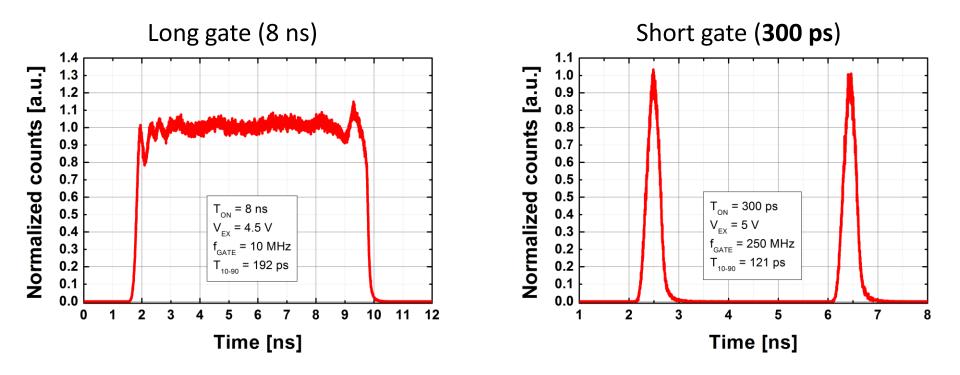

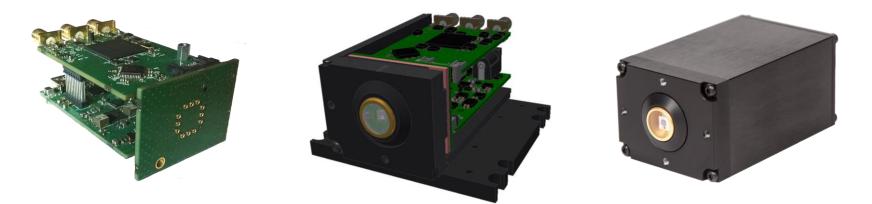

Compact module built around integrated fast-gated chip 34

Compact module based on integrated circuit & InGaAs/InP SPAD

| Maximum gate repetition rate | 250 MHz                      |  |

|------------------------------|------------------------------|--|

| Hold-off time                | 0.003 ÷ 1300 μs              |  |

| Gate width                   | 0.3 ÷ 1000 ns                |  |

| SPAD temperature             | 205 ÷ 290 K                  |  |

| Size                         | 40 x 50 x 70 mm <sup>3</sup> |  |

### Conclusions

## InGaAs/InP SPAD:

PoliMi experimental results (@  $V_{EX} = 5$  V):

- Low DCR

- Good detection efficiency

(~ 10<sup>3</sup> at 225 K) (30 % @ 1550 nm)

- Moderately low afterpulsing

- Low timing jitter

(FWHM < 90 ps)

## Circuits for high-count-rate InGaAs/InP SPAD system:

- SPAD with integrated quenching resistor

- GHz sinusoidal gate (SPAD-dummy balancing approach)

- Very low afterpulsing (< 1.5%)

- High count rate (> 600 Mcount/s)

- Compact modules based on fast-gating ASIC

- Trade-off between standard modules and GHz gating)

This work was funded by the projects EMPIR 14IND05 MIQC2 (H2020) and DARPA REVEAL:

#### Waiting for you at Single Photon Workshop 2019 in Milano!

ISSW 2018 – February 26, 2018 – alberto.tosi@polimi.it